研究チームは、ECRAM デバイスを使用したアナログ ハードウェアが人工知能の計算パフォーマンスを最大化できることを実証し、商業化の可能性を示しました。彼らの研究は、出版されたで科学の進歩。

生成 AI などのアプリケーションを含む AI テクノロジーの急速な進歩により、既存のデジタル ハードウェア (CPU、GPU、ASIC など) の拡張性が限界まで押し上げられています。そこで、AI計算に特化したアナログハードウェアの研究が盛んに行われています。

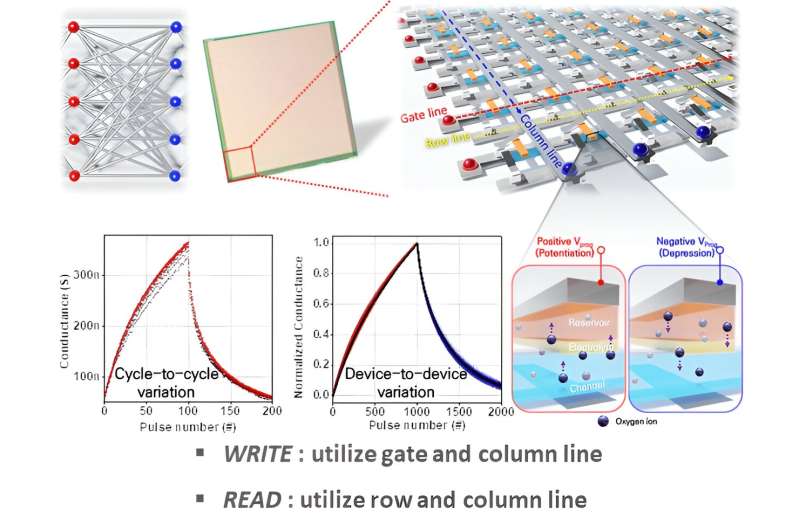

アナログハードウェアは、外部電圧または電流に基づいて半導体の抵抗を調整し、垂直に交差したクロスポイントアレイ構造を利用します。メモリデバイスAIの計算を並列処理します。特定の計算タスクや継続的なデータ処理に関してはデジタル ハードウェアに比べて利点がありますが、計算による学習と推論の多様な要件を満たすことは依然として困難です。

アナログ ハードウェア メモリ デバイスの限界に対処するため、材料科学工学科および半導体工学科の Seyoung Kim 教授らからなる研究チームは、電気化学ランダム アクセス メモリ (ECRAM) に焦点を当てました。電気伝導率イオンの移動と集中を通じて。

従来の半導体メモリとは異なり、これらのデバイスはデータの読み取りと書き込みの経路が独立した 3 端子構造を特徴としており、比較的低電力での動作が可能です。

研究チームは、64 × 64 アレイの 3 端子ベースの半導体を使用して ECRAM デバイスの製造に成功しました。実験の結果、チームのデバイスを組み込んだハードウェアは優れた電気特性とスイッチング特性を示し、高収量そして均一性。

さらに、チームは最先端のアナログベースの学習アルゴリズムである Tiki-Taka アルゴリズムをこの高収量ハードウェアに適用し、AI ニューラル ネットワークのトレーニング計算の精度を最大化することに成功しました。

注目すべきことに、研究者らはハードウェアトレーニングの「体重保持」特性が学習に与える影響を実証し、そのテクニックが過負荷にならないことを確認した。人工ニューラルネットワーク、この技術の商業化の可能性を強調しています。

これまで文献で報告されているアナログ信号の保存および処理用の ECRAM デバイスの最大配列は 10×10 であるため、この研究は重要です。研究者らは現在、各デバイスにさまざまな特性を備えたこれらのデバイスを最大規模で実装することに成功しています。

POSTECH の Seyoung Kim 教授は、「新しいメモリデバイス技術に基づく大規模アレイの開発と、アナログ固有の AI アルゴリズムの開発により、AI の計算パフォーマンスとエネルギー効率それは現在のデジタル手法をはるかに上回っています。」

詳細情報:Kyungmi Noh 他、Tiki-Taka アルゴリズムベースのアナログ深層学習アクセラレータのためのリテンションを意識したゼロシフト技術、科学の進歩(2024年)。DOI: 10.1126/sciadv.adl3350

引用:研究者らが高効率、低消費電力の人工知能のための次世代半導体技術を開発(2024年8月1日)2024 年 8 月 1 日に取得https://techxplore.com/news/2024-08-gen-semiconductor-technology-high-efficiency.html より

この文書は著作権の対象です。個人的な研究や研究を目的とした公正な取引を除き、書面による許可なく一部を複製することができます。コンテンツは情報提供のみを目的として提供されています。