Un equipo de investigación ha demostrado que el hardware analógico que utiliza dispositivos ECRAM puede maximizar el rendimiento computacional de la inteligencia artificial, mostrando su potencial de comercialización.Su investigación ha sidopublicadoenAvances científicos.

El rápido avance de la tecnología de IA, incluidas aplicaciones como la IA generativa, ha llevado la escalabilidad del hardware digital existente (CPU, GPU, ASIC, etc.) al límite.En consecuencia, existe una investigación activa sobre hardware analógico especializado para la computación de IA.

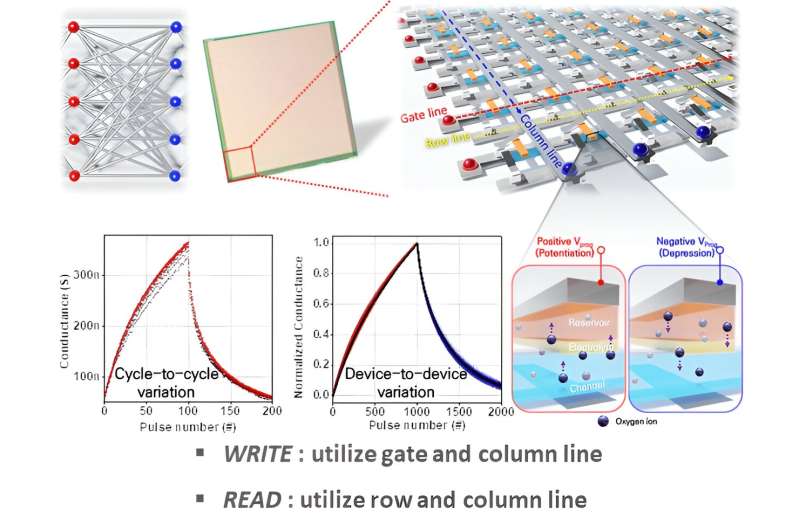

El hardware analógico ajusta la resistencia de los semiconductores en función del voltaje o la corriente externos y utiliza una estructura de matriz de puntos cruzados con cruces verticales.dispositivos de memoriapara procesar el cálculo de IA en paralelo.Aunque ofrece ventajas sobre el hardware digital para tareas computacionales específicas y procesamiento continuo de datos, cumplir con los diversos requisitos para el aprendizaje y la inferencia computacionales sigue siendo un desafío.

Para abordar las limitaciones de los dispositivos de memoria de hardware analógicos, el equipo de investigación, formado por el profesor Seyoung Kim del Departamento de Ciencia e Ingeniería de Materiales y el Departamento de Ingeniería de Semiconductores y otros, se centró en la memoria electroquímica de acceso aleatorio (ECRAM), que gestionaconductividad eléctricamediante el movimiento y la concentración de iones.

A diferencia de la memoria semiconductora tradicional, estos dispositivos cuentan con una estructura de tres terminales con rutas separadas para leer y escribir datos, lo que permite operar con una potencia relativamente baja.

En su estudio, el equipo fabricó con éxito dispositivos ECRAM utilizando semiconductores de tres terminales en una matriz de 64×64.Los experimentos revelaron que el hardware que incorporaba los dispositivos del equipo demostraba excelentes características eléctricas y de conmutación, además dealto rendimientoy uniformidad.

Además, el equipo aplicó el algoritmo Tiki-Taka, un algoritmo de aprendizaje analógico de vanguardia, a este hardware de alto rendimiento, maximizando con éxito la precisión de los cálculos de entrenamiento de redes neuronales de IA.

En particular, los investigadores demostraron el impacto de la propiedad de "retención de peso" del entrenamiento con hardware en el aprendizaje y confirmaron que su técnica no sobrecargaredes neuronales artificiales, destacando el potencial de comercialización de la tecnología.

Esta investigación es importante porque la mayor variedad de dispositivos ECRAM para almacenar y procesar señales analógicas reportada en la literatura hasta la fecha es 10×10.Los investigadores ahora han implementado con éxito estos dispositivos a mayor escala, con características variadas para cada dispositivo.

El profesor Seyoung Kim de POSTECH dijo: "Al desarrollar matrices a gran escala basadas en nuevas tecnologías de dispositivos de memoria y desarrollar algoritmos de IA analógicos específicos, hemos identificado el potencial para el rendimiento computacional de la IA yeficiencia energéticaque superan con creces los métodos digitales actuales."

Más información:Kyungmi Noh et al, Técnica de cambio cero con reconocimiento de retención para el acelerador de aprendizaje profundo analógico basado en el algoritmo Tiki-Taka,Avances científicos(2024).DOI: 10.1126/sciadv.adl3350

Citación:Investigadores desarrollan tecnología de semiconductores de próxima generación para inteligencia artificial de alta eficiencia y bajo consumo (2024, 1 de agosto)recuperado el 1 de agosto de 2024de https://techxplore.com/news/2024-08-gen-semiconductor-technology-high-efficiency.html

Este documento está sujeto a derechos de autor.Aparte de cualquier trato justo con fines de estudio o investigación privados, noparte puede ser reproducida sin el permiso por escrito.El contenido se proporciona únicamente con fines informativos.