La integración de chips electrónicos en dispositivos comerciales ha evolucionado significativamente en las últimas décadas, y los ingenieros han ideado diversas estrategias y soluciones de integración.Inicialmente, las computadoras contenían un procesador central o unidad central de procesamiento (CPU), conectado a unidades de memoria y otros componentes a través de vías de comunicación tradicionales, conocidas como interfaces de bus frontal (FSB).

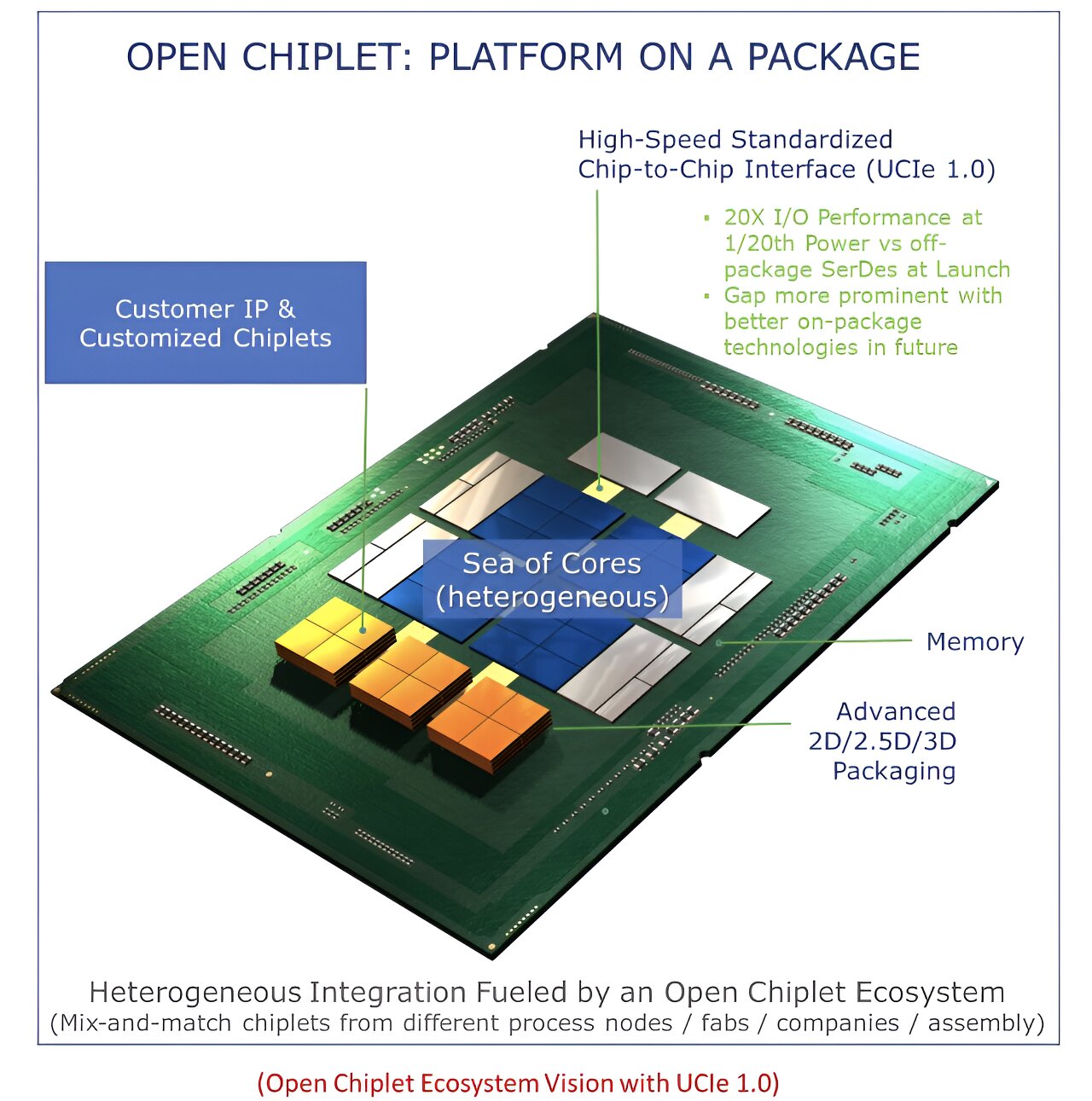

Sin embargo, los avances tecnológicos han permitido el desarrollo de nuevas arquitecturas de circuitos integrados (CI) basadas en múltiples chiplets y componentes electrónicos más sofisticados.Intel Corporation jugó un papel crucial en estos desarrollos, al introducir nuevas arquitecturas y especificaciones para el diseño de sistemas con múltiples chiplets empaquetados.

Investigadores de Intel Corporation Santa Clara esbozaron recientemente una nueva visión para aumentar aún más el rendimiento de los sistemas desarrollados siguiendo la interconexión universal de chiplet express (UCIe), una especificación para estandarizar las conexiones entre chiplets multifunción en el moderno sistema en paquete (SiP).Su enfoque propuesto, presentado en unpapelenElectrónica de la naturaleza, implica reducir la frecuencia en estos circuitos para aumentar su eficiencia energética y su rendimiento.

"Hemos estado impulsando tecnologías, como PCI-Express, CXL y UCIe, que son multigeneracionales", dijo el Dr. Debendra Das Sharma, miembro senior de Intel y codirector general de tecnologías de memoria y E/S, plataformas de datos y tecnología artificial.Intelligence Group de Intel Corporation, dijo a Tech Xplore."En el contexto de UCIe, después de completar UCIe 1.0, hemos estado buscando cómo ofrecer uno o dos pedidos más de rendimiento con, idealmente, un pedido menor de potencia por bit para satisfacer la demanda insaciable de rendimiento energéticamente eficiente".

Los avances en el desarrollo del silicio y la tecnología de embalaje han abierto nuevas posibilidades para reducir el espacio entre las protuberancias que conectan los chips individuales dentro de las placas de circuito, también conocidas como pasos de protuberancia.El objetivo principal del estudio realizado por el Dr. Das Sharma y sus colaboradores fue explorar estrategias que permitirían a los investigadores aumentar aún más el rendimiento y la eficiencia energética de los sistemas a medida que estos golpes continúan reduciéndose para las interconexiones en el paquete.

"La tendencia en los envases avanzados, incluido el 3D, es reducir el ángulo de impacto", afirmó el Dr. Das Sharma."El paso de golpe es la distancia mínima entre dos golpes que conectarán dos chiplets. Entonces, eso significa que obtenemos más cables entre dos chips a medida que se reduce el paso de golpe. La tendencia natural, principalmente derivada de interconexiones externas, es aumentar la frecuencia.Sin embargo, en este caso, dado que el número de cables aumenta, necesitamos reducir la frecuencia para que los circuitos encajen y obtengan menor potencia".

Como parte de su estudio, el Dr. Das Sharma y sus colegas llevaron a cabo análisis para explorar más a fondo los efectos de reducir la frecuencia en sistemas basados en chiplets empaquetados.Descubrieron que, a diferencia de las interfaces de conectividad de chips tradicionales, las tecnologías alineadas con UCIe se beneficiaron significativamente de una reducción en la frecuencia a medida que se redujeron los pasos de interconexión.

Específicamente, se encontró que las reducciones en la frecuencia mejoran tanto la eficiencia energética de los sistemas como su rendimiento general.En general, este artículo reciente identifica un nuevo enfoque valioso que podría contribuir a los avances futuros de los sistemas con circuitos interconectados a medida que su arquitectura subyacente evolucione aún más.

"Esperamos que la industria en general pueda beneficiarse de nuestro trabajo a través de la estandarización de la misma manera que lo hemos hecho en el pasado influyendo en las especificaciones estándar de la industria", añadió el Dr. Das Sharma."Personalmente, ahora planeo continuar trabajando para desarrollar interconexiones estándar de la industria como UCIe, CXL, PCIe como lo he hecho durante más de dos décadas. En el contexto de los chiplets y UCIe, el viaje acaba de comenzar y estoy entusiasmado con eloportunidades que tenemos por delante."

Más información:Debendra Das Sharma et al, Diseños de sistema en paquete tridimensional de alto rendimiento y eficiencia energética con interconexión de chiplet universal express,Electrónica de la naturaleza(2024).DOI: 10.1038/s41928-024-01126-y

© 2024 Red Ciencia X

Citación:Intel presenta un enfoque para aumentar la eficiencia energética y la confiabilidad de los ecosistemas de chiplets empaquetados (2024, 13 de marzo)recuperado el 13 de marzo de 2024de https://techxplore.com/news/2024-03-intel-approach-boost-power-efficiency.html

Este documento está sujeto a derechos de autor.Aparte de cualquier trato justo con fines de estudio o investigación privados, noparte puede ser reproducida sin el permiso por escrito.El contenido se proporciona únicamente con fines informativos.